## Pole Splitting in a Triode Gain Stage

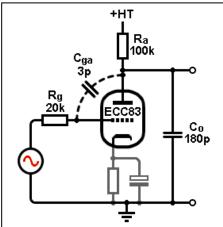

Fig. 1 shows an example gain stage using an ECC83 / 12AX7. The grid-anode capacitance is 3pF, made up from internal valve capacitance and external wiring capacitance. If the stage gain is about  $\times 60$  then  $C_{ga}$  will be multiplied and present a Miller capacitance ( $C_m$ ) of about 180pF. If we imagine the load capacitance  $C_o$  is not yet connected, then the  $20k\Omega$  grid stopper and 180pF Miller capacitance effectively form an RC filter, causing the frequency response to start rolling off at 44kHz, at a first-order rate. In other words, we have a pole ( $P_1$ ) at a frequency of:

$$f_{\rm Pl} = \frac{1}{2\pi C_{\rm m} R_{\rm g}} \tag{1.1}$$

Fig. 1: A simple gain stage with 180pF Miller capacitance and  $40k\Omega$  output resistance. What does its frequency response look like?

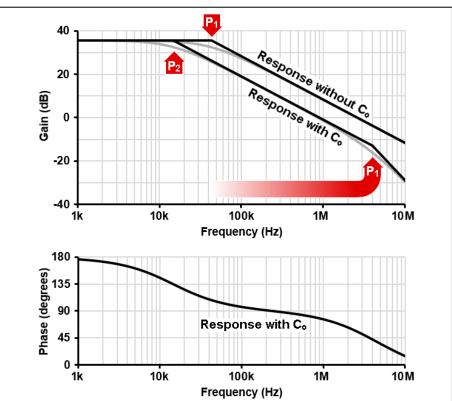

But what happens when we do include  $C_o$ ? If the stage has an output resistance  $R_o = 40 k\Omega$  and we load it with 180pF (which might represent the Miller capacitance of the next stage) then we might assume a new pole ( $P_2$ ) will be added a frequency of 22kHz. We might therefore expect the frequency response to start falling at a first order rate from 22kHz, followed by a second order rate from 44kHz. But we would be quite wrong! In fact there is an interaction between the two poles which causes  $P_2$  to be pushed somewhat lower in frequency, while  $P_1$  is pushed much higher –an effect known as pole splitting.

P<sub>2</sub> will occur at a frequency of:

$$f_{p2} = \frac{1}{2\pi C_o(R_o + R_g)}$$

(1.2)

And P<sub>1</sub> will be pushed up to:

$$f_{P1} = \frac{1}{2\pi C_{ga}(R_o||R_g)}$$

(1.3)

In this example the figures come out at  $P_2 = 14.7$ kHz and  $P_1 = 4$ MHz. Fig. 2 shows the resulting Bode plot of the circuit before adding the loading capacitor  $C_0$ , and after adding it (actual response shown faint).

Physically this pole-splitting effect happens because Miller capacitance only exists when the stage is able to produce an amplified signal at the anode, but when the stage is loaded by a significant capacitance the gain at high-frequency falls, and therefore the Miller multiplication effect falls too. Loading a stage with capacitance rather 'cancels out' the Miller effect.

The phase response with  $C_{\rm o}$  included is also shown in fig. 2. At low frequencies the phase shift is  $180^{\circ}$  because the stage is inverting.  $P_2$  then causes it to dive down to  $90^{\circ}$ , but it does not dive much further until very high frequencies where we approach  $P_1$  and beyond. In an amplifier with global feedback, phase shift spoils stability, so it is nice to discover that in this situation the phase change is not as rapid as we might have assumed if we had not known about the pole-splitting effect.

Fig. 2: Frequency response of the circuit in fig. X illustrated how adding the pole  $P_2$  causes the original pole  $P_1$  to be 'split' or pushed further away.